I used to be simply chatting with my chum Andy Nightingale, who’s VP of Product Administration and Advertising at Arteris IP.

What’s with the “IP” portion of the Arteris moniker? Properly, within the context of system-on-chip (SoC) gadgets, the time period mental property (IP) refers back to the useful blocks which are mixed to kind the ultimate gadget. The best way this often works is that a lot of the IPs—like processors, reminiscence, controllers, peripherals, and communications features—are sourced from trusted third-party distributors. This leaves the event staff free to deal with integrating every little thing while additionally creating a number of of their very own “secret sauce” IPs—like {hardware} accelerators or synthetic intelligence (AI) engines—that can make this SoC stand proud within the crowd with respect to any aggressive choices.

Along with offering chip-spanning network-on-chip (NoC) interconnect IP, which is used to attach the opposite IPs on the SoC collectively, Arteris IP additionally provides a collection of SoC integration automation and administration instruments, which enormously speeds the duty of pulling all of the IPs collectively and managing issues like their hundreds-of-thousands (typically thousands and thousands) of management and standing registers (CSRs).

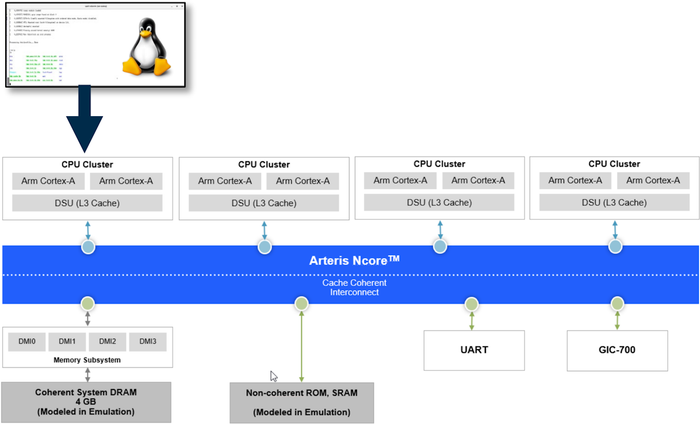

Andy was telling me that everybody at Arteris is at present bouncing off the partitions with pleasure as a result of they’ve simply introduced the three.6 launch of their Ncore coherent Community-on-Chip (NoC).

In some methods, Arteris jogs my memory of the ~160-year-old firm BASF, which is the biggest chemical producer on the earth. BASF used to have a well-known sequence of commercials, the underlying theme of which was, “We do not make the merchandise, we make them higher.” The purpose is that, outdoors of individuals in business, the general public was largely unaware of BASF’s existence, although folks had been cognizant of the merchandise created by different firms that had been primarily based on supplies provided by BASF. Equally, outdoors of SoC architects, designers, and verification engineers, most individuals have by no means heard of Arteris, although they’ve title recognition of the businesses creating the SoCs that depend on Arteris NoC know-how to make them work.

Simply to place this into perspective, someplace between 70% to 80% of SoCs utilized in superior driver-assistance system (ADAS) automotive functions depend on Arteris NoC know-how. Arteris additionally has a robust market presence and product providing in synthetic intelligence (AI) and machine studying (ML) system IP. Their silicon-proven interconnect IP has been utilized in an eye-watering ~3.5 billion SoCs shipped to this point, and this quantity is rising as I pen these phrases.

The ISO 26262 licensed Ncore coherent NoC provides all kinds of automated useful security (FuSa) options. ARTERIS

Except you might be an SoC designer your self, you might not be absolutely conversant with NoC ideas. Moreover, even SoC designers might not be acquainted with the coherent NoC choices from Arteris. So, let’s take a number of moments to set the scene.

Means again within the mists of time after I designed my first application-specific built-in circuit (ASIC) circa 1980, we didn’t even have the idea of IPs (or computer-aided design instruments, for that matter). I designed the complete gadget on the gate-and-register-level utilizing pencil and paper. Practical verification concerned different members of the staff gathering across the desk when you defined how your design carried out its magic within the hope they’d say, “Properly, that appears like it’ll work.” Equally, timing verification concerned my figuring out all of the important paths after which summing the delays on these paths by hand (I didn’t even have entry to a easy 4-function calculator—these had been reserved for executives who wanted them to calculate their expense accounts and milage allowances—it’s a marvel I’m not bitter).

By the Nineteen Nineties, distributors had been providing unassuming IPs, and ASIC/SoC designers had been connecting handfuls of those IPs utilizing easy bus buildings. By the early 2000s, IPs had been rather more complicated, SoCs featured a number of initiator and goal IPs, and designers moved to utilizing many-to-many crossbar change interconnect architectures. Circa the 2010s, when builders began to create SoCs containing lots of of extraordinarily massive and enormously complicated IPs, the crossbar idea grew to become more and more untenable as a consequence of silicon actual property utilization, routing congestion, and energy consumption issues. The answer was discovered within the type of NoCs.

The best method to visualize a NoC is as an on-chip community servicing anyplace from a number of to a number of lots of of supply (initiator) and vacation spot (goal) IPs. Some IPs can act as each initiators and targets, usually on the similar time. Completely different IPs from totally different distributors might make use of totally different communication protocols, together with APB, AHB, AXI, CHI, OCP, and so forth. Additionally, totally different IP interfaces might have totally different information widths operating at totally different clock frequencies. The answer is to have brokers (also referred to as “sockets”) that join the IPs to the NoC. The agent related to an initiator IP will packetize and serialize the information right into a impartial format earlier than handing it over to the NoC. The NoC will transport the packet to its vacation spot (goal) IP, the place that IP’s agent (socket) will de-serialize, de-packetize, and current the information within the kind (protocol, information width, clock frequency, and so forth.) required by that IP. Massive numbers of packets may be “in-flight” by means of the NoC on the similar time.

Designing a NoC is tough sufficient on a great day. It’s considerably harder to develop a coherent NoC. What will we imply by “coherent” on this context? Properly, first we want to ensure we’re all tap-dancing to the identical skirl of the bagpipes with respect to our understanding of cache, by which we imply small, quick reminiscences which are native to processor (and probably accelerator) IP cores.

The thought right here is that applications usually carry out a number of operations on the identical information and similar operations on intently positioned information. It takes time and energy for the SoC to entry information from off-chip DRAM gadgets. Thus, when a SoC processor core requests a bunch of directions and information from the principle reminiscence for the primary time, a replica is saved in its native cache for use for future operations. Actually, the core might have a number of ranges of cache, every with its personal copy of the identical information. Take into account a cluster of 4 processor cores, for instance. A standard situation is for every core to have its personal Stage 1 (L1) cache, for pairs of cores to share L2 caches, and for all 4 cores to share an L3 cache.

The idea behind cache coherency is to make sure that everybody (IP-wise) is aware of who’s holding the newest and biggest copy of every piece of information. A processor cluster is designed such that its cores robotically keep cache coherency. The issue arises when there are a number of such clusters—together with accelerator IPs with their very own caches—all of which want to keep up coherency. On this case, a coherent NoC should be used, the place the NoC basically implements an L4 cache, which is shared amongst all the opposite cores, and the NoC maintains coherency throughout the system.

Why don’t SoC design groups create their very own NoCs? If the reality be informed, some groups do try to do that, but it surely often ends in tears. Why? Properly, this can require a number of staff members devoting a big quantity of effort and time to the NoC portion of the challenge. The quantity of sources required will rely on the dimensions and complexity of the challenge, however a conservative estimate for a sophisticated coherent NoC is 50 engineering years. That’s loads of years. Particularly while you understand that, along with debugging their very own internally developed IPs (each in isolation and within the context of the remainder of the SoC), the staff may also find yourself spending an inordinate period of time debugging their internally developed NoC.

There’s additionally the issue of holding one’s personal NoC updated with evolving requirements and protocols. Take Arm processors as only one instance. Suppose a staff has spent the previous few years growing a NoC that, amongst different protocols, helps Arm’s CHI-B coherent interface. Unhappy to narrate, this gained’t work with the newest and biggest Armv9 Cortex automotive processor IPs, which assist solely CHI-E. “Oh expensive,” I can think about the staff members saying (or phrases to that impact).

Ncore 3.6 has been pre-validated with Armv9 automotive cores. ARTERIS

All this explains why the oldsters at Arteris are beaming with pleasure concerning the 3.6 product launch of their Ncore coherent NoC. Additionally, why the designers of SoCs from a number of markets—together with automotive, communications. enterprise computing, industrial, and medical—are tap-dancing within the streets on the information.

In a crunchy nutshell, Ncore accelerates trendy SoC designs and optimizes their efficiency by supporting heterogeneous processors and accelerators (e.g., Arm and RISC-V), a number of protocols (e.g., ACE, ACE-Lite, AXI, CHI-B, CHI-E), and a number of community topologies (e.g., ring, tree, mesh, torus).

Simply so as to add a few dollops of metaphorical cream on prime of the allegorical cake, Ncore is functionally protected (it’s ISO 26262 licensed, thereby serving to design groups handle the important calls for of automotive and industrial security functions with necessities from ASIL B to ASIL D) and it’s been pre-validated to be used with the newest and biggest Armv9 automotive cores.

Suffice it to say that Ncore cache coherent interconnect IP just isn’t your granny’s NoC. All I can say is that, again within the day after I was designing my very own ASICs, I might have discovered it exhausting to think about a NoC within the first place, and the considered a cache-coherent NoC like Ncore would have made (what I laughingly seek advice from as) my thoughts wobble on its gimbals with pleasure. How about you? What do you consider all of this?